## **Features**

- Wide Power Supply: +3.0V to +5.5V Single Supply

- Robust ESD Rating: >8kV HBM, >2kV CDM

- Green Product, MSOP8 Package

#### Video Filter:

- HDTV Video Filter Support Composite 1080p/60

- Optimized 6th-order Butterworth Video reconstruction filter:

- ♦ HD Channel: -3dB BW 52MHz

- Support Multiple Input Biasing:

- Transparent Clamping for DC restoration

- Provide 80-mV Level-Shift when DC-Coupled

- 6dB Gain(2V/V), Rail to Rail Output

- AC- or DC-Coupled Output Driving Dual Video Loads (75Ω)

#### **Comparator:**

- Fast Response Time: 40 ns Propagation Delay

- Internal Hysteresis Ensures Clean Switching

- Push-Pull, CMOS/TTL Compatible Output

- Same DC clamping circuit as video input.

## **Applications**

- Video Signal Amplification

- Set-Top Box Video Driver

- TV、DVD Player Video Buffer

- Video Buffer for Portable or USB-Powered Video Devices

- HDTV

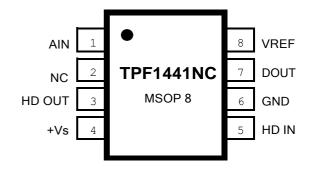

## **Pin Configuration (Top View)**

### **Description**

The TPF1441NC is a low power, 52M HD composite video filter and comparator on a single chip. Drawing less than 11.5mA supply current over the full operating temperature range, TP1441NC operates from a single 3.0V to 5.5V power supply.

TPF1441NC integrates high-performance low-cost 52MHz composite video reconstruction filter, however it has very low power consumption. The filter is sixth-order Butterworth characteristics that are useful as digital-to-analog converter (DAC) reconstruction filters or as analog-to-digital converter (ADC) anti-aliasing filters. The HD filters can actually support 720p/1080p CVI/TVI/AHD platform.

The TPF1441NC's on-board comparator incorporates 3PEAK's proprietary and patented design techniques to achieve the ultimate combination of high-speed (40ns propagation delay under 3.0~5.5V wide supply range) and low power consumption , The internal input hysteresis eliminates output switching due to internal input noise voltage, reducing current draw. The PUSH-PULL output supports rail-to-rail output swing, and interfaces with CMOS/TTL logic.

TPF1441NC is available in MSOP-8 package (TP1441NC-VR). Its operation temperature range is from  $-40^{\circ}$ C to  $+85^{\circ}$ C.

### **Related Resources**

AN-1201: Application notes of TPF1XX

| Pin Name | Pin Function                          |

|----------|---------------------------------------|

| AIN      | Non-Inverting Input of the Comparator |

| NC       | Not connect                           |

| HD OUT   | HD video output, LPF = 52 MHz         |

| +Vs      | Positive Power Supply                 |

| HD IN    | HD video input, LPF = 52 MHz          |

| GND      | Ground                                |

| DOUT     | Comparator Output                     |

| VREF     | Inverting Input of Comparator         |

# **Table of Contents**

| Features1                                            |

|------------------------------------------------------|

| Video Filter:                                        |

| Comparator:1                                         |

| Applications1                                        |

| Description1                                         |

| Related Resources1                                   |

| Pin Configuration (Top View)1                        |

| Revision History2                                    |

| Function Block                                       |

| Order Information                                    |

| Absolute Maximum Ratings*3                           |

| ESD, Electrostatic Discharge Protection              |

| Electrical Characteristics4                          |

| Electrical Characteristics-Comparator Part5          |

| Typical Performance Characteristics                  |

| Application Information                              |

| Internal Sync Clamp7                                 |

| Comparator Internal Clamp7                           |

| Droop Voltage and DC Restoration                     |

| Low Pass FilterSallen Key                            |

| Output Couple                                        |

| Output Drive Capability and Power Dissipation8       |

| Power Supply Bypassing Printed Circuit Board Layout9 |

| Package Outline Dimensions10                         |

| MSOP-8                                               |

| IMPORTANT NOTICE AND DISCLAIMER                      |

# **Revision History**

| Date       | Revision | Notes            |

|------------|----------|------------------|

| 2017/10/15 | Rev.A.0  | Initial Version  |

| 2018/10/30 | Rev.A.1  | Released Version |

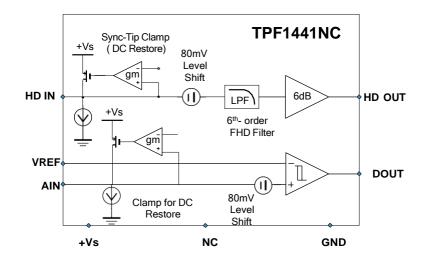

# **Function Block**

## **Order Information**

| Order Number | Operating Temperature Range | Package    | Marking Information | Transport Media, Quantity |

|--------------|-----------------------------|------------|---------------------|---------------------------|

| TPF1441NC-VR | -40 to 85°C                 | 8-Pin MSOP | TPF1441NC           | Tape and Reel, 3000       |

## **Absolute Maximum Ratings\***

|                                      | Parameters                                  | Value                       | Units      |

|--------------------------------------|---------------------------------------------|-----------------------------|------------|

| Power Supply, V <sub>DD</sub> to GND |                                             | 6.0                         | V          |

| V <sub>IN</sub> Input Voltage        |                                             | V <sub>DD</sub> + 0.3V to 0 | GND - 0.3V |

| Ιo                                   | Output Current                              | 65                          | mA         |

| TJ                                   | T <sub>J</sub> Maximum Junction Temperature |                             | °C         |

| T <sub>A</sub>                       | T <sub>A</sub> Operating Temperature Range  |                             | °C         |

| T <sub>STG</sub>                     | Storage Temperature Range                   | -65 to 150                  | °C         |

| TL                                   | TL Lead Temperature (Soldering 10 sec)      |                             | °C         |

| θ <sub>JA</sub>                      | 8-Lead MSOP                                 | 210                         | °C/W       |

\* **Note:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

(1) This data was taken with the JEDEC low effective thermal conductivity test board.

(2) This data was taken with the JEDEC standard multilayer test boards.

## **ESD**, Electrostatic Discharge Protection

| Symbol | Parameter                | Condition              | Minimum Level | Unit |

|--------|--------------------------|------------------------|---------------|------|

| HBM    | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 | 8             | kV   |

| CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 | 2             | kV   |

## **Electrical Characteristics**

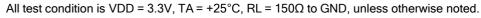

All test condition is VDD = 3.3V, TA = +25°C, RL = 150 $\Omega$  to GND, unless otherwise noted.

| SYMBOL                | PARAMETER                       |                                                                    | CONDITIONS                                                             | MIN  | ТҮР   | MAX  | UNITS    |

|-----------------------|---------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------|------|-------|------|----------|

| Input Electric        | al Specifications               |                                                                    |                                                                        |      | 1     |      | <u> </u> |

| V <sub>DD</sub>       | Supply Voltage R                | lange                                                              |                                                                        | 3.0  |       | 5.5  | V        |

|                       |                                 | · (I ) (1)                                                         | $V_{\text{DD}}$ = 3.3V, $V_{\text{IN}}$ = 500mV, no load               |      | 9     |      | mA       |

| I <sub>DD</sub>       | Quiescent current $(I_Q)^{(1)}$ |                                                                    | $V_{\text{DD}}$ = 5.0V, $V_{\text{IN}}$ = 500mV, no load               |      | 10    |      | mA       |

| ICLAMP-DOWN           | Clamp Discharge                 | Current                                                            | V <sub>IN</sub> =300mV, measure current                                | 0.6  | 2.64  | 4.8  | μA       |

| I <sub>CLAMP-UP</sub> | Clamp Charge C                  | urrent                                                             | V <sub>Y</sub> = -0.2V                                                 |      | -1.7  |      | mA       |

| V <sub>CLAMP</sub>    | Input Voltage Cla               | 1mp <sup>(2)</sup>                                                 | I <sub>Y</sub> = -100μΑ                                                | 0    |       | +40  | mV       |

| R <sub>IN</sub>       | Input Impedance                 |                                                                    | 0.5V < V <sub>Y</sub> < 1V                                             |      | 3     |      | MΩ       |

| AV                    | Voltage Gain                    |                                                                    | V <sub>IN</sub> =0.5V,1V or 2V<br>R <sub>L</sub> =150Ω to GND          | 5.91 | 6.02  | 6.06 | dB       |

| V <sub>OLS</sub>      | Output Level Shit               | vel Shift Voltage V <sub>IN</sub> = 0V, no load, input referred 54 |                                                                        | 54   | 80    | 124  | mV       |

| V <sub>OL</sub>       | Output Voltage Low Swing        |                                                                    | $V_{IN}$ = -0.3V, R <sub>L</sub> =75 $\Omega$                          |      | 0.058 |      | V        |

| V <sub>OH</sub>       | Output Voltage High Swing       |                                                                    | $V_{\text{IN}}$ = 3.3V, $R_{\text{L}}$ =75 $\Omega$ to GND (dual load) |      | 3.24  |      | V        |

| PSRR Power Supply I   | Dowor Supply Do                 | viaction Datio                                                     | $\Delta V_{DD}$ = 3.3V to 3.6V                                         |      | 61    |      | dB       |

|                       | Power Supply Re                 | ejection Ratio                                                     | $\Delta V_{\text{DD}}$ = 5.0V to 5.5V, 50Hz                            |      | 67    |      | dB       |

| 1                     | Oh et einelten met              | ant                                                                | $V_{IN}$ = 2V, 10 $\Omega$ , output to GND                             |      | 65    |      | mA       |

| I <sub>SC</sub>       | Short-circuit curre             |                                                                    | $V_{\text{IN}}$ =0.1V, output short to $V_{\text{DD}}$                 |      | 65    |      | mA       |

| AC Electrical         | Specifications                  |                                                                    |                                                                        |      |       |      |          |

| f <sub>-1dB</sub>     | -1dB Bandwidth                  | HD Channel                                                         | R <sub>L</sub> =150Ω                                                   |      | 41.5  |      | MHz      |

| f <sub>-3dB</sub>     | -3dB Bandwidth                  | HD Channel                                                         | R <sub>L</sub> =150Ω                                                   |      | 52    |      | MHz      |

| dG                    | Differential Gain               |                                                                    | Video input range 1V                                                   |      | 0.4   |      | %        |

| dP                    | Differential Phase              |                                                                    | Video input range 1V                                                   |      | 0.7   |      | o        |

| IHD                   | Total Harmonic                  | HUUnannei                                                          | f=10MHz, $V_{OUT}$ =1.4 $V_{PP}$                                       |      | 0.15  |      | %        |

|                       | Distortion                      |                                                                    | f=22MHz, $V_{OUT}$ = 1.4 $V_{PP}$                                      |      | 0.6   |      | %        |

| D/DT                  | Group Delay                     | Group Delay HD Channel                                             | f = 100kHz to 27MHz                                                    |      | 2.2   |      | ns       |

|                       | Variation                       |                                                                    | f = 100kHz to 60MHz                                                    |      | 6.0   |      | ns       |

| SNR                   | Signal-to-Noise<br>Ration       | HD Channel                                                         | f= 100kHz to 60MHz                                                     |      | 64    |      | dB       |

| R <sub>OUT_AC</sub>   | Output Impedance                | e                                                                  | f = 10MHz                                                              |      | 0.5   |      | Ω        |

\*Note: (1). 100% tested at TA=25°C.

(2). Comparator Clamp has the same specification.

# **Electrical Characteristics-Comparator Part**

All test condition is VDD = 3.3V, TA = +25°C, CL =15pF, unless otherwise noted.

| SYMBOL              | PARAMETER                         | CONDITIONS             | MIN                  | ТҮР | MAX                  | UNITS |

|---------------------|-----------------------------------|------------------------|----------------------|-----|----------------------|-------|

| V <sub>DD</sub>     | Supply Voltage                    |                        | 3                    |     | 5.5                  | V     |

| Vos                 | Input Offset Voltage Note 1       | V <sub>CM</sub> = 1.2V |                      | 80  |                      | mV    |

| V <sub>os</sub> TC  | Input Offset Voltage Drift Note 1 | V <sub>CM</sub> = 1.2V | 0.3                  |     | μV/°C                |       |

| V <sub>HYST</sub>   | Input Hysteresis Voltage Note 1   | V <sub>CM</sub> = 1.2V |                      | 6   |                      | mV    |

| V <sub>OH</sub>     | High-Level Output Voltage         | I <sub>OUT</sub> =-1mA | V <sub>DD</sub> -0.3 |     |                      | V     |

| V <sub>OL</sub>     | Low-Level Output Voltage          | I <sub>OUT</sub> =1mA  |                      |     | V <sub>SS</sub> +0.3 | V     |

| I <sub>SC</sub>     | Output Short-Circuit Current      | Sink or source current |                      | 5   |                      | mA    |

| t <sub>R</sub>      | Rising Time                       |                        |                      | 7   |                      | ns    |

| t <sub>F</sub>      | Falling Time                      |                        |                      | 7   |                      | ns    |

| T <sub>PD+</sub>    | Propagation Delay (Low-to-High)   | VREF =1.65V            |                      | 36  |                      | ns    |

| T <sub>PD-</sub>    | Propagation Delay (High-to-Low)   | VREF =1.65V            |                      | 42  |                      | ns    |

| T <sub>PDSKEW</sub> | Propagation Delay Skew            | VREF =1.65V            |                      | 4   |                      | ns    |

**Note 1:** The input offset voltage is the average of the input-referred trip points. The input hysteresis is the difference between the input-referred trip points.

## **Typical Performance Characteristics**

# **Application Information**

The TPF1441NC is targeted for systems that require 1 channel high-definition (HD) video outputs. Although it can be used for numerous other applications, the needs and requirements of the video signal are the most important design parameters of the TPF1441NC. The TPF1441NC incorporates many features not typically found in integrated video parts while consuming very low power.

#### **Internal Sync Clamp**

The typical embedded video DAC operates from a ground referenced single supply. This becomes an issue because the lower level of the sync pulse output may be at a 0V reference level to some positive level. The problem is presenting a 0V input to most single supply driven amplifiers will saturate the output stage of the amplifier resulting in a clipped sync tip and degrading the video image. A larger positive reference may offset the input above its positive range.

The TPF1441NC features an internal sync clamp and offset function to level shift the entire video signal to the best level before it reaches the input of the amplifier stage. These features are also helpful to avoid saturation of the output stage of the amplifier by setting the signal closer to the best voltage range.

The simplified block diagram of the TPF1441NC is on Page-2. The AC coupled video sync signal is pulled negative by a current source at the input of the comparator amplifier. When the sync tip goes below the comparator threshold the output comparator is driven negative, The PMOS device turns on clamping sync tip to near ground level. The network triggers on the sync tip of video signal.

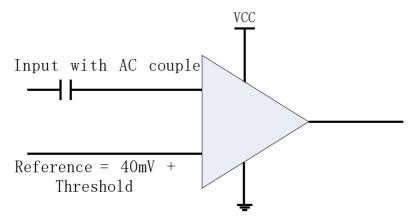

### **Comparator Internal Clamp**

TPF1441NC integrates a comparator, which supports UTC function monolithically. Because of the distortion of the control signal transmitted over a long cable, the rising/falling edges would become slower and the amplitude would be attenuated. Furthermore the DC component may be shifted due to inconsistent DC ground level between sending and receiving devices. In a traditional design, the reference of the comparator needs to be manually changed accordingly. In order to solve this application problem, TPF1441NC implements a new feature on the input of comparator which clamps the bottom level of the input signal to 40.0 mV. Therefore, there is no need to consider the DC shift issue when choosing reference level, making the choice of reference level easier. Note that, to use this feature, the input must be AC-coupled and the capacitor selection is based on the control signal bandwidth. Typically a 0.1uF capacitor is used..

## **Droop Voltage and DC Restoration**

Selection of the input AC-coupling capacitance is based on the system requirements. A typical sync tip width of a 64 $\mu$ s NTSC line is 4 $\mu$ s during which clamp circuit restores its DC level. In the remaining 60 $\mu$ s period, the voltage droops because of a small constant 2.0 $\mu$ A sinking current. If the AC-coupling capacitance is 0.1 $\mu$ F, the maximum droop voltage is about 1mV which is restored by the clamp circuit. The maximum pull-up current of the clamp circuit is 1.7mA. For a 4 $\mu$ s sync tip width and 0.1 $\mu$ F capacitor, the maximum restoration voltage is about 80mV.

The line droop voltage will increase if a smaller AC-coupling capacitance is used. For the same reason, if larger capacitance is used the line droop voltage will decrease. Table 1 is droop voltage and maximum restoration voltage of the clamp for typical capacitance.

| CAP VALUE<br>(nF) | DROOP IN 60µs<br>(mV) | CHARGE IN 4µs<br>(mV) |

|-------------------|-----------------------|-----------------------|

| 100               | 1.2                   | 68                    |

| 1,000             | 0.12                  | 6.8                   |

|  | Table 1. | Maximum restoration | voltage and droop | o voltage of | r signals for | different capacitance |

|--|----------|---------------------|-------------------|--------------|---------------|-----------------------|

|--|----------|---------------------|-------------------|--------------|---------------|-----------------------|

#### Low Pass Filter--Sallen Key

The Sallen Key is a classic low pass configuration. This provides a very stable low pass function, and in the case of the TPF1441NC, the six-pole roll-off at around 52MHz. The six-pole function is accomplished with an RC low pass network placed in series with and before the Sallen Key.

#### **Output Couple**

TPF1441NC output could support both "AC Couple" and "DC Couple", if use "AC Couple", this capacitor is typically between 220- $\mu$ F and 1000- $\mu$ F, although 470- $\mu$ F is common. This value of this capacitor must be this large to minimize the line tilt (droop) and/or field tilt associated with ac-coupling as described previously in this document.

The TPF1441NC internal sync clamp makes it possible to DC couple the output to a video load, eliminating the need for any AC coupling capacitors, thereby saving board space and additional expense for capacitors. This makes the TPF1441NC extremely attractive for portable video applications. Additionally, this solution completely eliminates the issue of field tilt in the lower frequency. The trade-off is the supply current could be bigger. Typical load current for AC coupled is around 1mA, compared to typical 11.5mA used when DC coupling.

### **Output Drive Capability and Power Dissipation**

With the high output drive capability of the TPF1441NC, it is possible to exceed the +125°C absolute maximum junction temperature under certain load current conditions. Therefore, it is important to calculate the maximum junction temperature for an application to determine if load conditions or package types need to be modified to assure operation of the amplifier in a safe operating area. The maximum power dissipation allowed in a package is determined according to Equation:

$$PD_{MAX} = \frac{T_{JMAX} - T_{AMAX}}{JA}$$

Where: TJMAX = Maximum junction temperature TAMAX = Maximum ambient temperature

OJA = Thermal resistance of the package

The maximum power dissipation actually produced by an IC is the total quiescent supply current times the total power supply voltage, plus the power in the IC due to the load, or: for sourcing:

$$PD_{MAX} = V_{s} \times I_{SMAX} + (V_{s} - V_{OUT}) \times \frac{V_{OUT}}{R_{L}}$$

Where:

VS = Supply voltage

ISMAX = Maximum quiescent supply current

VOUT = Maximum output voltage of the application

RLOAD = Load resistance tied to ground

By setting the two PDMAX equations equal to each other, we can solve the output current and RLOAD to avoid the device overheat.

### **Power Supply Bypassing Printed Circuit Board Layout**

As with any modern operational amplifier, a good printed circuit board layout is necessary for optimum performance. Lead lengths should be as short as possible. The power supply pin must be well bypassed to reduce the risk of oscillation. For normal single supply operation, a single 4.7µF tantalum capacitor in parallel with a 0.1µF ceramic capacitor from VS+ to GND will suffice.

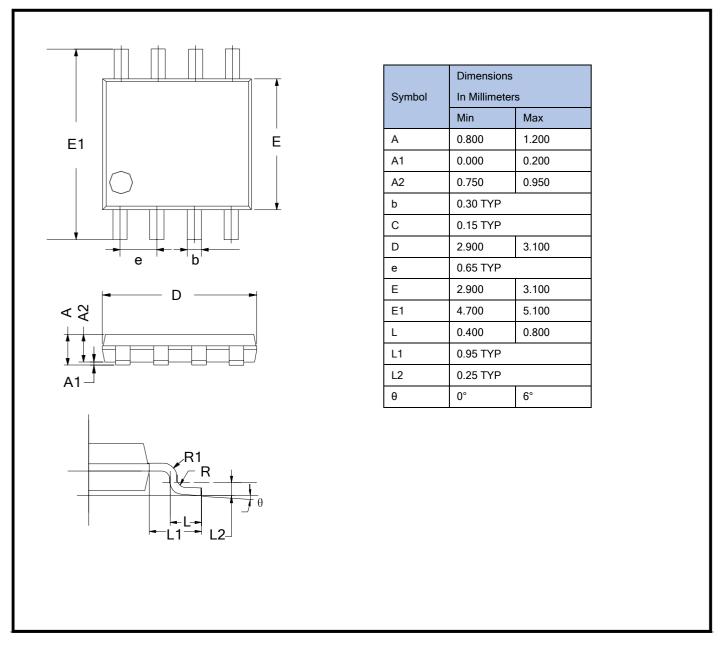

# **Package Outline Dimensions**

**MSOP-8**

### **IMPORTANT NOTICE AND DISCLAIMER**

Copyright© 3PEAK 2012-2023. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.