### **Features**

Input Voltage Range: 1.7 V to 5.5 VOutput Voltage Range: 0.6 V to 5.3 V

±1.5% Output Accuracy over Line Regulation, Load Regulation, and Operating Temperature Range

500-mA Maximum Output Current

Low Dropout Voltage: 150 mV Typical at 500 mA

High PSRR:

- 89 dB at 1 kHz

- 63 dB at 100 kHz

55 dB at 1 MHz

• 5.7-µV<sub>RMS</sub> Output Voltage Noise

· Excellent Transient Response

Stable with a 4.7-µF or Larger Ceramic Output Capacitor

Over-Current and Over-Temperature Protection

Output Reverse Current Protection

Junction Temperature Range: –40°C to +125°C

Package Options: DFN2X2-8

## **Applications**

Portable and Battery-Powered Equipment

Mobile Phones and Tablets

Digital Cameras and Audio Devices Power Supply

Video Surveillance

## **Description**

The TPL9053-S series products are 500-mA high PSRR, ultra-low noise, and low dropout linear regulators with high-output accuracy. The TPL9053-S series products support adjustable output voltage ranging from 0.6 V to 5.3 V with an external resistor divider, and is stable with a 4.7- $\mu$ F or larger ceramic output capacitor.

The TPL9053-S series products have high PSRR with 89 dB at 1 kHz and 5.7- $\mu$ V<sub>RMS</sub> ultra-low noise. These features make TPL9053-S series products very suitable for noise-sensitive applications with high noise from the previous stage power supply, such as high-performance analog devices, or high-definition imaging equipment. Output shortage protection and thermal overload protection circuits improve the reliability under heavy load conditions.

The TPL9053-S series products provide a DFN2X2-8 package with guaranteed operating junction temperature range ( $T_J$ ) from  $-40^{\circ}$ C to  $+125^{\circ}$ C.

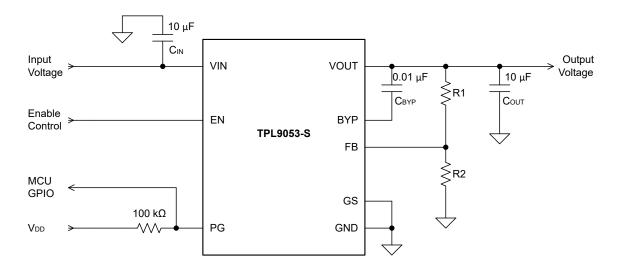

## **Typical Application Circuit**

## **Table of Contents**

| Features                                | 1  |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             | 1  |

| Typical Application Circuit             | 1  |

| Product Family Table                    | 3  |

| Revision History                        | 3  |

| Pin Configuration and Functions         | 4  |

| Specifications                          | 5  |

| Absolute Maximum Ratings (1)            | 5  |

| ESD, Electrostatic Discharge Protection | 5  |

| Recommended Operating Conditions        | 5  |

| Thermal Information                     | 5  |

| Electrical Characteristics              | 6  |

| Typical Performance Characteristics     | 8  |

| Detailed Description                    | 10 |

| Overview                                | 10 |

| Functional Block Diagram                | 10 |

| Feature Description                     | 10 |

| Application and Implementation          | 13 |

| Application Information                 | 13 |

| Typical Application                     | 13 |

| Layout                                  | 15 |

| Layout Guideline                        | 15 |

| Tape and Reel Information               | 16 |

| Package Outline Dimensions              | 17 |

| DFN2X2-8                                | 17 |

| Order Information                       | 18 |

| IMPORTANT NOTICE AND DISCLAIMER         | 19 |

# **Product Family Table**

| Order Number     | Output Voltage (V) | Package  |  |  |

|------------------|--------------------|----------|--|--|

| TPL9053AD-DF4R-S | Adjustable         | DFN2X2-8 |  |  |

## **Revision History**

| Date                                                                | Revision     | Notes                                          |  |  |  |

|---------------------------------------------------------------------|--------------|------------------------------------------------|--|--|--|

| 2019/08/31                                                          | Rev.Pre      | Preliminary Version                            |  |  |  |

| 2020/04/08                                                          | Rev.A.0      | Initial Released                               |  |  |  |

| 2024/07/05                                                          | 7/05 Rev.A.1 | Added Tape and Reel Information                |  |  |  |

| 2021/07/05                                                          |              | 2. Added description of PG pin and PG function |  |  |  |

| 2022/10/10 Rev.A.2 Updated the format of Package Outline Dimensions |              |                                                |  |  |  |

www.3peak.com 3 / 20 DA20221001A2

# **Pin Configuration and Functions**

TPL9053-S Series DFN2X2-8 Package Top View

Table 1. Pin Functions: TPL9053-S

| Pin No. | Pin Name | I/O                                                                                      | Description                                                                                                                                                 |  |  |

|---------|----------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7       | BYP      | I                                                                                        | Bypass input pin. Connect a 10-nF ceramic capacitor from BYP to OUT to reduce output noise.                                                                 |  |  |

| 3       | EN       | I                                                                                        | Regulator enable pin. Drive EN high to turn on the regulator, and drive EN low to turn off the regulator. For automatic startup, connect EN to IN directly. |  |  |

| 6       | FB       | Output voltage feedback pin. Connect to a resistor divider to adjust the output voltage. |                                                                                                                                                             |  |  |

| 2       | GND      | -                                                                                        | Ground reference pin. Connect GND pin to PCB ground plane directly.                                                                                         |  |  |

| 4       | GS       | _                                                                                        | Internal reference pin. MUST connect GS pin to PCB ground plane directly.                                                                                   |  |  |

| 1       | IN       | I                                                                                        | Input voltage pin. Bypass IN to GND with a 10 μF or greater capacitor.                                                                                      |  |  |

| 8       | OUT      | 0                                                                                        | Regulated output voltage pin. Bypass OUT to GND with a 4.7 µF or greater capacitor.                                                                         |  |  |

| 5 PG I  |          | Open-drain power-good output pin. Connect a 100-kΩ pull-up resistor to                   |                                                                                                                                                             |  |  |

<sup>(1)</sup> Thermal Pad MUST be connected to PCB ground plane directly.

www.3peak.com 4 / 20 DA20221001A2

## **Specifications**

### Absolute Maximum Ratings (1)

|                  | Parameter                           | Min  | Max | Unit |

|------------------|-------------------------------------|------|-----|------|

| EN, IN           |                                     | -0.3 | 6   | V    |

| BYP, FB, GS      | BYP, FB, GS, OUT, PG                |      | 6   | V    |

| TJ               | Junction Temperature Range          | -40  | 150 | °C   |

| T <sub>STG</sub> | Storage Temperature Range           | -65  | 150 | °C   |

| TL               | Lead Temperature (Soldering 10 sec) |      | 260 | °C   |

<sup>(1)</sup> Stresses beyond the Absolute Maximum Ratings may permanently damage the device.

### **ESD, Electrostatic Discharge Protection**

| Symbol | Parameter                | Condition                  | Minimum Level | Unit |

|--------|--------------------------|----------------------------|---------------|------|

| НВМ    | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1) | ±6            | kV   |

| CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 (2) | ±1.5          | kV   |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

|                  | Parameter                  | Min | Тур | Max       | Unit |

|------------------|----------------------------|-----|-----|-----------|------|

| IN               |                            | 1.7 |     | 5.5       | V    |

| EN               |                            | 0   |     | $V_{IN}$  | V    |

| OUT              |                            | 0   |     | 5.5       | V    |

| BYP, FB, PG      |                            | 0   |     | $V_{OUT}$ | V    |

| C <sub>BYP</sub> |                            | 1   |     | 100       | nF   |

| C <sub>OUT</sub> | Соит                       |     |     |           | μF   |

| ESR              |                            | 1   |     | 100       | mΩ   |

| TJ               | Junction Temperature Range | -40 |     | 125       | °C   |

| P <sub>D</sub>   | Power Dissipation          | 0   |     | 400       | mW   |

### **Thermal Information**

| Package Type | θυΑ | θυς  | Unit |

|--------------|-----|------|------|

| DFN2X2-8     | 120 | 20.3 | °C/W |

www.3peak.com 5 / 20 DA20221001A2

<sup>(2)</sup> All voltage values are with respect to GND.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Electrical Characteristics**

All test condition:  $V_{IN} = V_{OUT(NOM)} + 1 \text{ V}$ ,  $C_{IN} = 10 \ \mu\text{F}$ ,  $C_{OUT} = 10 \ \mu\text{F}$ ,  $-40^{\circ}\text{C} \le T_{J} \le +125^{\circ}\text{C}$ , unless otherwise noted.

|                         | Parameter                             | Test Conditions                                                                     | Min   | Тур   | Max   | Unit              |

|-------------------------|---------------------------------------|-------------------------------------------------------------------------------------|-------|-------|-------|-------------------|

| Supply I                | Input Voltage and Current             | •                                                                                   |       |       |       |                   |

| $V_{\text{IN}}$         | Input Supply Voltage Range            |                                                                                     | 1.7   |       | 5.5   | V                 |

| I <sub>GND</sub>        | Ground Pin Current                    | I <sub>OUT</sub> = 0 mA                                                             |       | 130   | 180   | μA                |

| I <sub>SHDN</sub>       | Shutdown Current                      | EN = GND                                                                            |       | 0.05  | 2     | μA                |

| Enable I                | nput Voltage and Current              |                                                                                     |       |       |       |                   |

| V <sub>IN(EN)</sub>     | EN Logic-input High Level (enable)    |                                                                                     | 1.2   |       | Vin   | V                 |

| V <sub>IL(EN)</sub>     | EN Logic-input Low Level (disable)    |                                                                                     | 0     |       | 0.4   | V                 |

| I <sub>EN</sub>         | EN Pin Leakage Current                | V <sub>EN</sub> = 5 V                                                               |       | 1     | 2     | μΑ                |

| Regulate                | ed Output Voltage and Current         |                                                                                     |       |       |       |                   |

| V <sub>OUT</sub>        | Output Voltage Accuracy               | –40°C ≤ T <sub>J</sub> ≤ +125°C                                                     | -1.5% |       | 1.5%  |                   |

|                         | Line Regulation                       | V <sub>IN</sub> = V <sub>OUT(NOM)</sub> + 1 V to 5.5 V                              |       | 1     |       | mV/V              |

| $\Delta V_{\text{OUT}}$ | Load Regulation                       | V <sub>IN</sub> = V <sub>OUT(NOM)</sub> + 1 V,<br>I <sub>OUT</sub> = 1 mA to 500 mA |       | 0.005 |       | mV/mA             |

|                         |                                       | V <sub>IN</sub> ≥ 3.6 V, I <sub>OUT</sub> = 100 mA                                  |       | 30    | 60    | mV                |

| $V_{DO}^{(1)}$          | Dropout Voltage                       | V <sub>IN</sub> ≥ 3.6 V, I <sub>OUT</sub> = 500 mA                                  |       | 150   | 280   | mV                |

|                         |                                       | V <sub>IN</sub> = 1.7 V, I <sub>OUT</sub> = 500mA                                   |       | 300   |       | mV                |

| lout                    | Output Voltage                        | V <sub>OUT</sub> in regulation                                                      | 0     |       | 500   | mA                |

| I <sub>LIM</sub>        | Output Current Limit                  | $V_{OUT} = 0.9 \times V_{OUT(NOM)}$                                                 | 550   | 720   |       | mA                |

| Isc                     | Short-circuit to Ground Current Limit | $V_{OUT}$ is forced to $\leq 50$ mV, $T_A = 25$ °C                                  |       | 100   |       | mA                |

|                         |                                       | I <sub>OUT</sub> = 20 mA, f = 100 Hz                                                |       | 82    |       | dB                |

| DODD                    |                                       | I <sub>OUT</sub> = 20 mA, f = 1 kHz                                                 |       | 89    |       | dB                |

| PSRR                    | Power Supply Rejection Ratio          | I <sub>OUT</sub> = 20 mA, f = 100 kHz                                               |       | 63    |       | dB                |

|                         |                                       | I <sub>OUT</sub> = 20 mA, f = 1 MHz                                                 |       | 55    |       | dB                |

| V <sub>N</sub>          | Output Noise Voltage                  | I <sub>OUT</sub> = 150 mA, BW = 100 Hz to<br>80 kHz                                 |       | 5.7   |       | μV <sub>RMS</sub> |

| tstr                    | Start-up Time                         | V <sub>OUT</sub> reaches 95% of nominal output voltage after EN = high              |       | 0.8   | 3     | ms                |

| Feedbac                 | ck and Bypass                         |                                                                                     | 1     | 1     | 1     | 1                 |

| V <sub>FB</sub>         | Output Feedback Voltage               |                                                                                     | 0.591 | 0.6   | 0.609 | V                 |

| I <sub>FB</sub>         | Output Feedback Leakage<br>Current    | V <sub>IN</sub> = 5.5 V, V <sub>FB</sub> = 0.75 V, TA = 25°C                        |       | 0.001 | 0.1   | μA                |

| I <sub>BYP</sub>        | BYP Pin Current during Startup        |                                                                                     |       | 1     |       | mA                |

|                         |                                       | 1                                                                                   | 1     | I.    | I .   | 1                 |

www.3peak.com 6 / 20 DA20221001A2

| Parameter                                                    |                              | Test Conditions                                                                              | Min | Тур  | Max | Unit             |  |  |  |

|--------------------------------------------------------------|------------------------------|----------------------------------------------------------------------------------------------|-----|------|-----|------------------|--|--|--|

| Power G                                                      | Power Good                   |                                                                                              |     |      |     |                  |  |  |  |

| V                                                            | PG Threshold                 | OUT rising until PG is toggled                                                               | 88% | 91%  | 94% | V <sub>OUT</sub> |  |  |  |

| $V_{PG,TH}$                                                  | PG Hysteresis                |                                                                                              |     | 2.5% |     | Vouт             |  |  |  |

| $V_{PG,IL}$                                                  | PG Voltage Low               | 1 mA to PG pin                                                                               |     | 10   | 100 | mV               |  |  |  |

| I <sub>PG</sub>                                              | PG Pin Leakage Current       |                                                                                              | -1  | 0.01 | 1   | μA               |  |  |  |

| Transien                                                     | t Characteristics            |                                                                                              |     |      |     |                  |  |  |  |

| $\Delta V_{	ext{OUT}}$                                       | Line Transient               | $V_{IN}$ = 3.8 V to 4.8 V, rising and falling slew rate is 1 V/5 $\mu$ s, $I_{OUT}$ = 500 mA |     | 3    |     | mVpp             |  |  |  |

|                                                              |                              | I <sub>OUT</sub> = 2 mA to 100 mA in 1 μs                                                    |     | 10   |     | mVpp             |  |  |  |

|                                                              | Load Transient               | I <sub>OUT</sub> = 50 mA to 500 mA in 1 μs                                                   |     | 20   |     | mVpp             |  |  |  |

| V <sub>REV,TH</sub> IN-OUT Reverse Voltage Turnoff Threshold |                              | V <sub>OUT</sub> – V <sub>IN</sub> when the input voltage falls                              |     | 19   |     | mV               |  |  |  |

| Temperature Range                                            |                              |                                                                                              | ·   |      |     | ·                |  |  |  |

| _                                                            | Thermal Shutdown Temperature |                                                                                              |     | 165  |     | °C               |  |  |  |

| T <sub>SD</sub>                                              | Thermal Shutdown Hysteresis  |                                                                                              |     | 15   |     | °C               |  |  |  |

<sup>(1)</sup> The dropout voltage is defined as  $V_{DO} = V_{IN} - V_{OUT}$ . For  $V_{IN} \ge 3.6$  V condition, the dropout voltage is measured when the FB pin voltage is forced at 0.58 V. For  $V_{IN} = 1.7$  V condition, the dropout voltage is guaranteed by design.

www.3peak.com 7 / 20 DA20221001A2

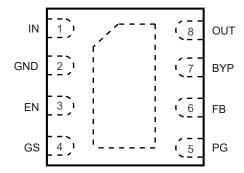

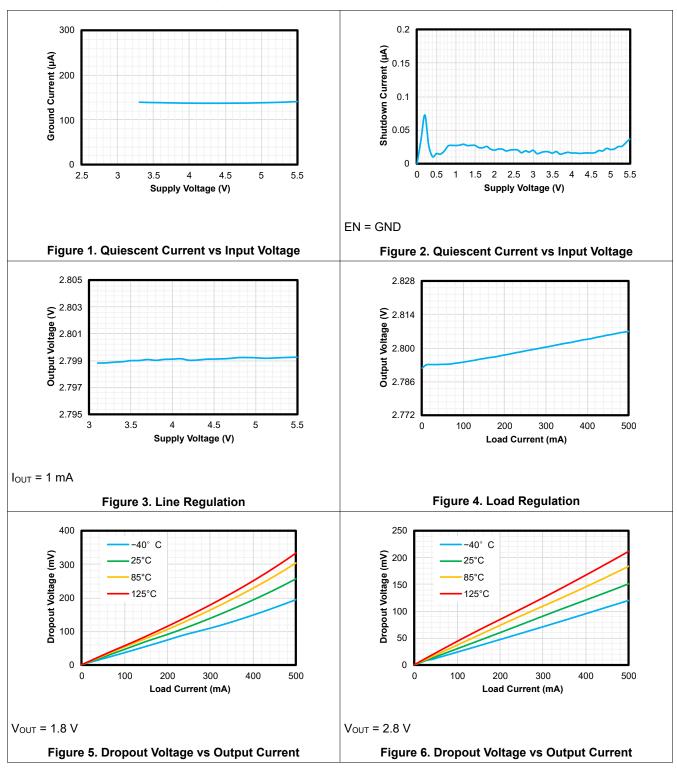

### **Typical Performance Characteristics**

All test condition:  $V_{IN} = 5 \text{ V}$ ,  $V_A = +25^{\circ}\text{C}$ , unless otherwise noted.

www.3peak.com 9 / 20 DA20221001A2

### **Detailed Description**

#### Overview

The TPL9053-S series products are 500-mA high PSRR, ultra-low noise, and low dropout linear regulators with high-output accuracy. The TPL9053-S series products support adjustable output voltage ranging from 0.6 V to 5.3 V with an external resistor divider and is stable with a 4.7-µF or larger ceramic output capacitor.

The TPL9053-S series products have high PSRR with 89 dB at 1 kHz and 5.7-µVRMS ultra-low noise. These features make TPL9053-S series products very suitable for noise-sensitive applications with high noise from the previous stage power supply, such as high-performance analog devices, or high-definition imaging equipment. Output shortage protection and thermal overload protection circuits improve the reliability under heavy load conditions.

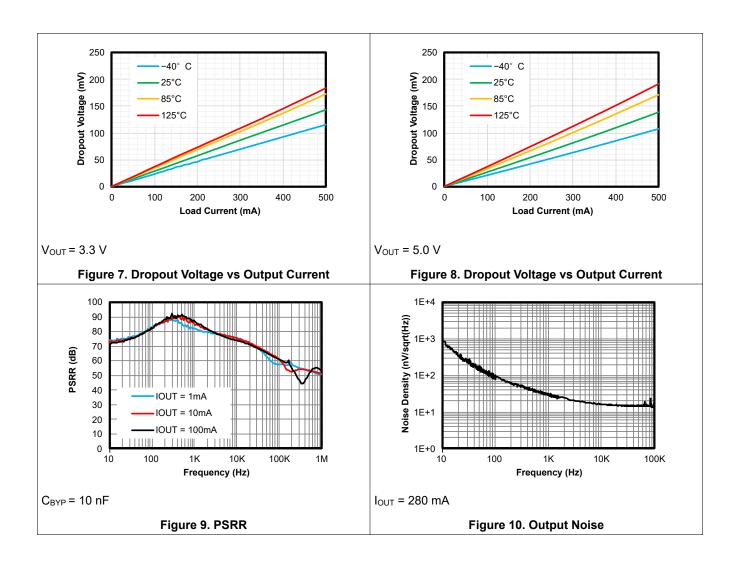

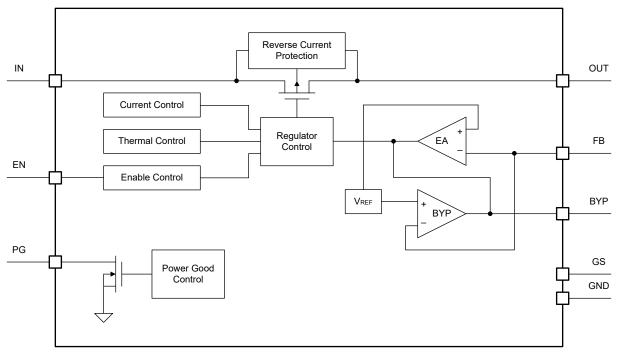

### **Functional Block Diagram**

Figure 11. Functional Block Diagram

#### **Feature Description**

#### Enable (EN)

The enable pin (EN) is active high. Connect this pin to the GPIO of an external processor or digital logic control circuit to enable and disable the device. Or connect this pin to the IN pin for self-bias applications.

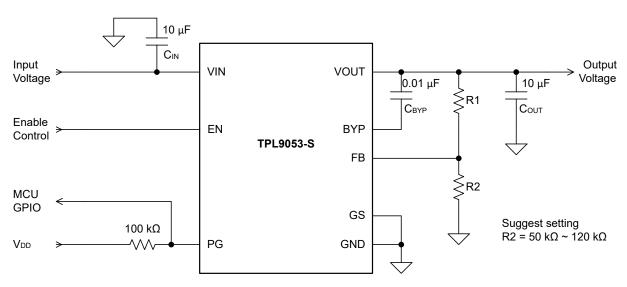

#### Adjustable Output Voltage (FB and OUT)

The output voltage range of the TPL9053-S series can be set from 0.6 V to 5.3 V by selecting different external resistors as shown in Figure 12. Use Equation 1 to calculate the output voltage. Suggest setting the resistance of lower feedback resistor R2 between 50 k $\Omega$  and 120 k $\Omega$  to minimize FB input bias current error.

www.3peak.com 10 / 20 DA20221001A2

$$V_{OUT} = V_{FB} \times \left(1 + \frac{R1}{R2}\right) \tag{1}$$

Where the feedback voltage  $V_{FB}$  is 0.6 V.

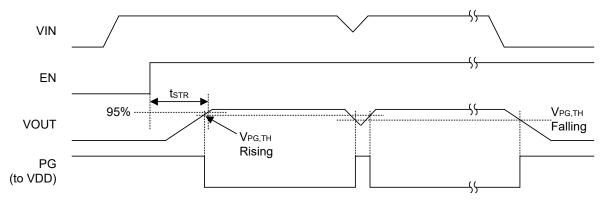

#### **Output Voltage Ramp-up Slew Rate Control**

To avoid the start-up inrush current, the TPL9053-S series integrates an output voltage ramp-up slew rate control. When the input voltage is ready and the device-enable signal asserts, the output voltage of TPL9053-S ramps up with a fixed slew rate. Under the room temperature condition, it takes  $800~\mu s$  from the rising edge of enable signal to the  $V_{OUT}$  reaching 95% of nominal output voltage. This start-up time is independent of the output capacitor and BYP capacitor, and the maximum 3-ms start-up time occurs under the -40°C ambient temperature condition.

#### Bypass (BYP)

The TPL9053-S series provides the BYP pin to reduce the regulator output noise and offers a feedback path to improve the transient response. Suggest connecting a capacitor from 1 nF to 100 nF from BYP to OUT.

#### Power-Good Indicator (PG)

The TPL9053-S series integrates an open-drain output power good indicator. After the regulator startup, the PG pin keeps high impendence until the output voltage reaches the power good threshold  $V_{PG,TH}$  (91% of  $V_{OUT}$ ). When the output voltage is higher than  $V_{PG,TH}$ , the PG pin turns to a low output impedance, and PG is pulled down to a low voltage level to indicate the output voltage is ready.

Figure 12 shows the power good indicator status after the device starts up.

Figure 12. Power Good Indication

#### **Reverse-Current Protection**

The TPL9053-S series provides the RCP protection to prevent output reverse current. If large capacitors had been used at the output, there would be a large reverse current when the input voltage is lower than the output voltage. The TPL9053-S series can shut off the regulator and body diode path to prevent the device being damaged from reverse current fault.

#### **Over-Current Protection and Short-to-Ground Protection**

The TPL9053-S series integrates an internal current limit that helps to protect the regulator during fault conditions.

- When the output is pulled down below the regulated voltage, over-current protection starts to work and limits the output current to 720 mA (typ).

- When the output is shorted to ground directly or pulled down below 50 mV, short-to-ground protection starts to work and limit the output current to 100 mA (typ).

www.3peak.com 11 / 20 DA20221001A2

Under the over-current conditions, the internal junction temperature ramps up quickly. When the junction temperature is high enough, it will cause the over-temperature protection.

#### **Over-Temperature Protection**

The recommended operating junction temperature range is -40°C to 125°C. When the junction temperature is between 125°C and the thermal shutdown (TSD) threshold, the regulator can still work well, but will reduce the device lifetime for long-term use.

The over-temperature protection works when the junction temperature exceeds the thermal shutdown (TSD) threshold, which turns off the regulator immediately. Until when the device cools down and the junction temperature falls below the thermal shutdown threshold minus thermal shutdown hysteresis, the regulator turns on again.

www.3peak.com 12 / 20 DA20221001A2

## **Application and Implementation**

#### Note

Information in the following application sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### **Application Information**

The TPL9053-S devices are a series of 500-mA high PSRR, ultra-low noise, low-dropout linear regulators. The following application schematic shows a typical usage of the TPL9053-S series.

### **Typical Application**

Figure 13 shows the typical application circuit of the TPL9053-S series.

Figure 13. Typical Application Circuit

#### **Input Capacitor and Output Capacitor**

3PEAK recommends adding a 10- $\mu$ F or greater capacitor with a 0.1- $\mu$ F bypass capacitor in parallel at the IN pin to keep the input voltage stable. The voltage rating of the capacitors must be greater than the maximum input voltage.

To ensure loop stability, the TPL9053-S series requires an output capacitor of 4.7  $\mu$ F or greater. 3PEAK recommends selecting an X5R- or X7R-type 10- $\mu$ F ceramic capacitor with low ESR over temperature.

Both input capacitors and output capacitors must be placed as close to the device pins as possible.

#### **Power Dissipation**

During normal operation, the LDO junction temperature should not exceed 125°C. Using below equations to calculate the power dissipation and estimate the junction temperature.

The power dissipation can be calculated using Equation 2.

www.3peak.com 13 / 20 DA20221001A2

$$P_{D} = (V_{IN} - V_{OUT}) \times I_{OUT} + V_{IN} \times I_{GND}$$

(2)

The junction temperature can be estimated using Equation 3.  $\theta_{\text{JA}}$  is the junction-to-ambient thermal resistance.

$$T_{J} = T_{A} + P_{D} \times \theta_{JA} \tag{3}$$

www.3peak.com 14 / 20 DA20221001A2

## Layout

### **Layout Guideline**

- Both input capacitors and output capacitors must be placed to the device pins as close as possible.

- It is recommended to bypass the input pin to ground with a 0.1-µF bypass capacitor. The loop area formed by the bypass capacitor connection, the IN pin, and the GND pin of the system must be as small as possible.

- It is recommended to use wide trace lengths or thick copper weight to minimize I×R drop and heat dissipation.

www.3peak.com 15 / 20 DA20221001A2

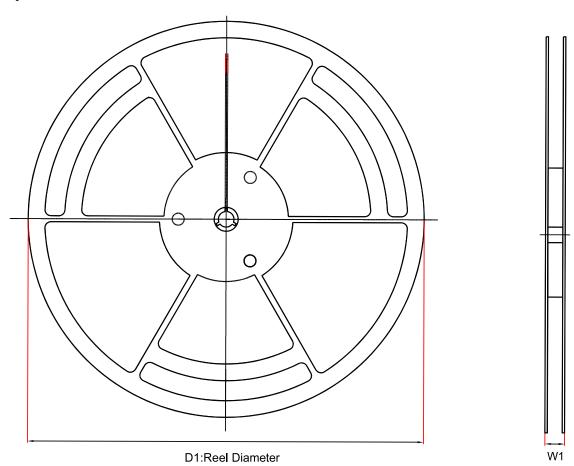

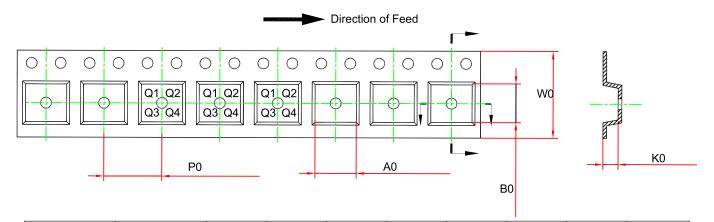

# **Tape and Reel Information**

| Order Number         | Package  | D1 (mm) | W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P0 (mm) | W0 (mm) | Pin1<br>Quadrant |

|----------------------|----------|---------|---------|---------|---------|---------|---------|---------|------------------|

| TPL9053AD-<br>DF4R-S | DFN2X2-8 | 180.0   | 13.1    | 2.3     | 2.3     | 1.1     | 4.0     | 8.0     | Q1               |

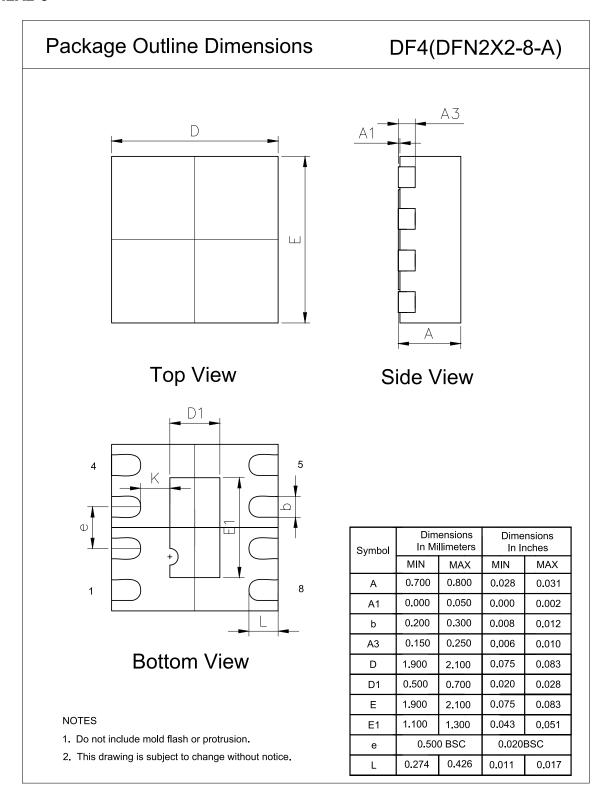

## **Package Outline Dimensions**

### **DFN2X2-8**

### **Order Information**

| Order Number     | Operating Temperature<br>Range | Package  | Marking Information | MSL | Transport Media, Quantity | Eco Plan |

|------------------|--------------------------------|----------|---------------------|-----|---------------------------|----------|

| TPL9053AD-DF4R-S | −40 to 125°C                   | DFN2X2-8 | L905                | 3   | Tape and Reel, 3000       | Green    |

**Green**: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

www.3peak.com 18 / 20 DA20221001A2

#### IMPORTANT NOTICE AND DISCLAIMER

Copyright<sup>©</sup> 3PEAK 2012-2023. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.

www.3peak.com 19 / 20 DA20221001A2

This page intentionally left blank